Das hat Mark Papermaster 2022 auf dem Financial Analyst Day präsentiert:

Mark Papermaster sagt die Varianten von Zen 5 kommen als 4 nm oder 3 nm.

Dan McNamara (EPYC) hat sich nicht zu Turin geäußert und Saeid Moshekelani hatte bei Zen 5 immer "Advanced Node" stehen.

Ich hätte eigentlich auch erwartet, dass AMD auf dem 5 nm Node bleibt, aber Mark Papermaster sagt ganz klar dass Zen 5 auch als 3 nm kommt.

Wenn man sich Zen 4 anschaut dann haben wir 3 Dies mit Zen 4:

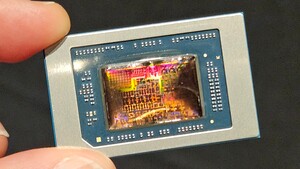

- APU Phoenix

- Zen 4 CCD

- Zen 4c CCD

Ich denke dass es grundsätzlich bei dieser Aufteilung bleibt.

Bei Strix Point erwarte ich N4P. N3E skaliert weder bei IO noch bei Cache.

Bei den CCDs kann man nun lange diskutieren. Mark Paper Master hat 3 nm angekündigt und ich sehe jetzt keinen Vorteil einen CCD in 3 nm und den anderen in 4 nm zu machen. Also lassen wir uns überraschen.

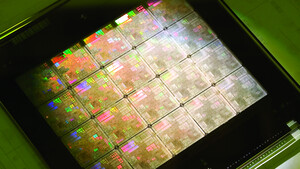

TSMC hat angekündigt dass N3E Ende 2023 in HVM geht, da sollte bis Mitte 2023 jede Menge Zeit für AMD bleiben.

Zum Thema 3D V-Cache: Wenn es 4 nm wird sollte die versionen MIT 3D V-Cache bald bereit stehen.

Ich habe nichts gefunden wann TSMC SoIC für 3 nm bereitsteht. Und ohne TSMC SoIC wird es keinen 3D V-Cache geben.

Die Anzeichen verdichten sich, dass 16 Zen 5 CCD und 12 Zen 5c CCD auf dem Sockel S5 untergebracht werden. Das verschlechtert die Bandbreite je Kern, da wir nach wie vor 12 DDR-5 Kanäle haben.

SemiAnalysis hatte erklärt, dass AMD wegen dem Routing des Infinityfabric auf dem Substrat nur 8 Zen 4c CCD unternbringen konnte. Schaun wir Mal wie es AMD schafft bei Turin Dense 12 Zen 5c CCDs unterzubringen.